La souveraineté numérique ne se décrète pas, elle se fabrique : la victoire se joue sur le wafer de silicium, à l’échelle de l’atome.

- Le rendement de production (yield) est le principal nerf de la guerre, déterminant la viabilité économique de toute une filière.

- La maîtrise de la contamination particulaire et la précision des processus de gravure et de dépôt constituent le véritable champ de bataille industriel.

Recommandation : Aborder chaque étape de la nanofabrication non pas comme une simple opération technique, mais comme un maillon stratégique de l’autonomie technologique.

L’écho médiatique et politique autour de la souveraineté numérique est assourdissant. Plans d’investissement massifs, alliances stratégiques, discours sur la nécessité de relocaliser la production de semi-conducteurs : tout converge vers une prise de conscience géopolitique. On évoque les gigafactories, les « Chips Acts » et la dépendance critique envers l’Asie. Ces discussions sont nécessaires, mais elles masquent une réalité plus fondamentale, une vérité de terrain que tout directeur d’usine de puces connaît intimement.

La souveraineté numérique n’est pas une abstraction. Elle ne se gagne pas dans les ministères, mais dans l’environnement le plus contrôlé au monde : la salle blanche. C’est une bataille industrielle, une guerre de précision où chaque geste, chaque processus et chaque particule de poussière a des conséquences économiques et stratégiques. L’enjeu n’est pas seulement d’avoir les machines, mais de posséder la maîtrise opératoire, cette compétence collective à exécuter des processus d’une complexité inouïe avec une fiabilité quasi parfaite. C’est la différence entre posséder une Formule 1 et savoir la piloter pour gagner un championnat.

Mais si la véritable clé n’était pas la capacité à investir des milliards, mais la capacité à maîtriser une myriade de détails nanoscopiques ? Cet article propose de descendre dans la « salle des machines » de notre autonomie technologique. Nous allons disséquer les verrous critiques de la nanofabrication, de la sculpture atomique à la guerre du rendement, pour comprendre où se niche réellement la compétence qui fonde la souveraineté numérique de demain.

Cet article plonge au cœur des défis techniques et humains qui définissent la capacité d’une nation à produire les cerveaux de notre monde numérique. Le sommaire ci-dessous vous guidera à travers ces étapes critiques où se joue notre indépendance technologique.

Sommaire : Les défis opérationnels de la nanofabrication au service de l’autonomie stratégique

- Comment sculpter la matière atome par atome pour réparer un circuit microscopique ?

- Comment faire tenir un film de métal de 3 atomes d’épaisseur sur du plastique ?

- Attaque chimique liquide ou bombardement ionique : quel choix pour des murs verticaux parfaits ?

- Le grain de poussière invisible qui tue votre puce à 1000 euros

- Problème de coût : comment passer de 50% à 99% de puces fonctionnelles par wafer ?

- Faisceau d’électrons ou photolithographie : quelle technique pour le prototypage rapide de nanostructures ?

- Le geste brusque qui coûte 50 000 € de puces électroniques en une seconde

- Comment la lithographie descendante peut-elle encore descendre sous les 5 nanomètres ?

Comment sculpter la matière atome par atome pour réparer un circuit microscopique ?

Imaginez un sculpteur capable de retirer la matière grain par grain. En nanofabrication, cet outil existe : c’est le Faisceau d’Ions Focalisé, ou FIB (Focused Ion Beam). Cette technologie ne se contente pas de graver ; elle opère une véritable chirurgie nanométrique. Un faisceau d’ions lourds, comme le gallium, est accéléré et focalisé sur une zone de quelques nanomètres carrés. L’impact de ces ions pulvérise la matière de la cible avec une précision absolue, permettant de couper des tranchées, de percer des trous ou de déposer de nouveaux matériaux avec une finesse inégalée.

La puissance du FIB réside dans sa double capacité : usiner et imager. En balayant la surface avec un courant ionique plus faible, le système produit une image de la topographie avec une clarté stupéfiante. Les systèmes actuels peuvent atteindre une résolution d’imagerie de 5 nanomètres, permettant de visualiser les structures que l’on vient de créer. C’est cet aller-retour constant entre l’action et l’observation qui rend le FIB indispensable pour le contrôle qualité et l’analyse de défaillances.

L’application la plus stratégique est sans doute la préparation d’échantillons pour la microscopie électronique en transmission (TEM). Pour analyser un défaut au cœur d’une puce, il faut pouvoir en extraire une lamelle de quelques dizaines de nanomètres d’épaisseur, pile à l’endroit du problème. Le FIB est la seule technologie capable d’effectuer cette découpe avec la précision requise. Comme le souligne un rapport de JEOL, un fabricant d’équipements de pointe, cette technique est particulièrement indispensable pour l’analyse des défaillances des dispositifs semiconducteurs. Elle permet de disséquer un composant pour comprendre pourquoi il a échoué, une information capitale pour améliorer le rendement des lignes de production.

Comment faire tenir un film de métal de 3 atomes d’épaisseur sur du plastique ?

Le dépôt de couches minces est un pilier de la microélectronique. Il s’agit de recouvrir une surface, le substrat, d’un film de matériau dont l’épaisseur peut se mesurer en quelques atomes seulement. Si le processus est bien maîtrisé sur des substrats rigides comme le silicium, il devient un défi majeur sur des substrats flexibles, tels que les polymères utilisés dans l’électronique souple (écrans pliables, capteurs corporels). Le problème n’est pas seulement de déposer le métal, mais de garantir son adhésion parfaite et durable.

Un film métallique de quelques nanomètres d’épaisseur ne se comporte pas comme un matériau massif. Les forces inter-atomiques et les propriétés de surface dominent. Le défi est de créer une interface stable entre le métal et le polymère, deux matériaux aux propriétés physiques et chimiques radicalement différentes. Une mauvaise adhésion se traduira par des fissures, un décollement ou une dégradation rapide des performances électriques sous l’effet de contraintes mécaniques comme la flexion.

Pour y parvenir, les ingénieurs déploient des trésors d’ingéniosité. Les techniques de dépôt physique en phase vapeur (PVD), comme la pulvérisation cathodique, sont optimisées pour contrôler l’énergie des atomes métalliques lorsqu’ils heurtent le substrat. Une énergie trop faible ne crée pas de liaison forte ; une énergie trop forte peut endommager la surface fragile du polymère. Souvent, une couche d’adhésion de quelques angströms (par exemple, du chrome ou du titane) est déposée en premier pour servir de « colle » atomique entre le polymère et la couche métallique fonctionnelle (or, cuivre).

L’illustration ci-dessus montre la complexité visuelle d’un tel film. Les motifs iridescents ne sont pas une couleur intrinsèque, mais le résultat de l’interférence de la lumière sur une couche dont l’épaisseur est de l’ordre de la longueur d’onde lumineuse. C’est la signature visible d’un contrôle de processus à l’échelle nanométrique. La maîtrise de cette interface fragile est une condition sine qua non pour le développement de la prochaine génération d’appareils électroniques portables et intégrés.

Attaque chimique liquide ou bombardement ionique : quel choix pour des murs verticaux parfaits ?

Une fois qu’un matériau est déposé sur le wafer, l’étape suivante consiste à en retirer certaines parties pour dessiner les motifs du circuit. C’est la gravure (etching). Deux grandes familles de techniques s’opposent : la gravure humide (wet etching) et la gravure sèche (dry etching). D’un point de vue industriel et stratégique, le choix entre les deux n’est pas anodin, car il détermine directement la densité d’intégration des composants, et donc la puissance de la puce finale.

La gravure humide utilise des bains chimiques (acides ou bases) pour dissoudre le matériau. C’est une méthode relativement simple et peu coûteuse, mais elle a un inconvénient majeur : elle est isotrope. Cela signifie que l’acide attaque la matière dans toutes les directions à la même vitesse, creusant non seulement en profondeur mais aussi latéralement, sous le masque de protection. Le résultat est un profil de gravure aux bords arrondis ou inclinés, ce qui limite la proximité entre deux motifs adjacents. Pour des applications ne demandant pas une haute résolution, c’est suffisant.

Pour l’électronique de pointe, c’est la gravure sèche qui s’impose. Cette technique, qui inclut le bombardement ionique (comme le RIE – Reactive Ion Etching), se déroule dans un plasma. Des ions sont accélérés et projetés perpendiculairement à la surface du wafer. Cette attaque est hautement anisotrope, ou directionnelle. Les ions bombardent le fond de la tranchée sans toucher les parois latérales. On obtient ainsi des murs parfaitement verticaux et des motifs aux dimensions fidèles à celles du masque. C’est cette verticalité qui permet de densifier les circuits à l’extrême.

Le tableau suivant, basé sur les principes décrits par des spécialistes comme les experts en faisceaux d’ions de JEOL, résume les différences fondamentales entre ces deux approches.

| Caractéristique | Gravure chimique (wet) | Bombardement ionique (dry) |

|---|---|---|

| Directionnalité | Isotrope (omnidirectionnelle) | Anisotrope (directionnelle) |

| Profil des murs | Arrondis/inclinés | Verticaux/droits |

| Application | Grandes surfaces | Structures nanométriques |

En clair, la souveraineté sur les puces les plus avancées passe obligatoirement par la maîtrise des procédés de gravure sèche. C’est un savoir-faire complexe, qui exige un contrôle parfait des gaz, de la pression et des champs électromagnétiques dans la chambre à plasma. Un profil de gravure qui dévie de quelques degrés peut mettre en court-circuit des millions de transistors.

Le grain de poussière invisible qui tue votre puce à 1000 euros

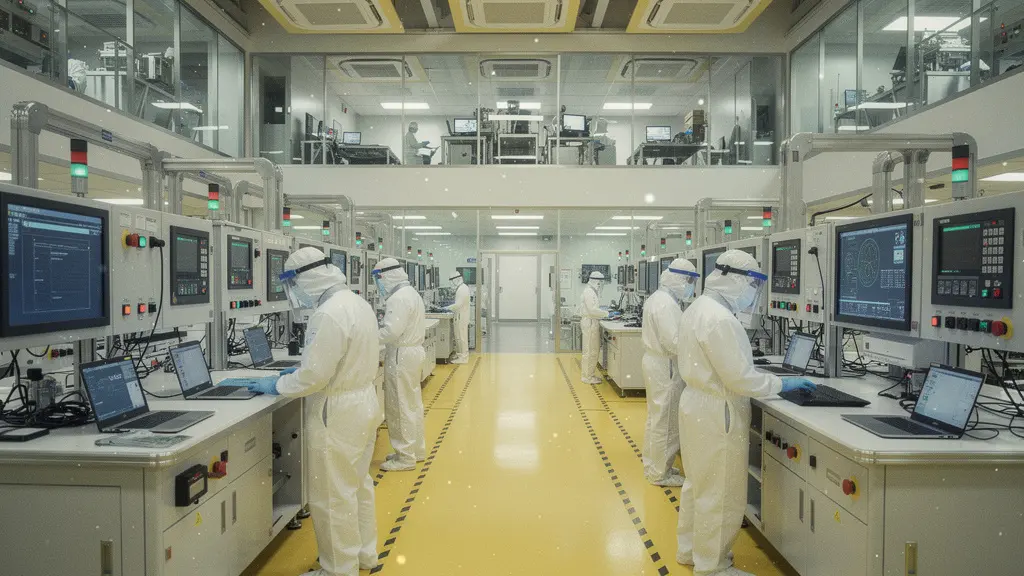

En microélectronique, l’ennemi le plus redoutable est invisible : c’est la particule. Un simple grain de poussière, une fibre de vêtement ou même un micro-organisme, mesurant moins d’un micromètre, peut suffire à détruire une puce entière. Quand les transistors mesurent quelques dizaines d’atomes de large, une particule agit comme un rocher tombant au milieu d’une ville miniature, créant des courts-circuits ou des interruptions de connexion. C’est ce que j’appelle la tyrannie de la particule. C’est pour la combattre qu’ont été inventées les salles blanches.

Une salle blanche (ou cleanroom) est un environnement où la concentration de particules en suspension dans l’air est contrôlée à un niveau extrêmement bas. La propreté y est définie par des normes ISO. Pour la fabrication des puces les plus avancées, on travaille dans des environnements de classe ISO 3, voire ISO 1. À titre de comparaison, l’air que nous respirons en ville contient plusieurs millions de particules de plus de 0,5 µm par mètre cube. Dans une salle blanche respectant la norme la plus stricte, une salle blanche classe ISO 1 ne tolère qu’une seule particule de plus de 0,5 µm par mètre cube d’air.

Pourtant, la technologie ne fait pas tout. La principale source de contamination dans une salle blanche, c’est l’être humain. C’est pourquoi les opérateurs portent des combinaisons intégrales, des masques, des gants et des sur-bottes. Chaque mouvement est calculé pour minimiser la génération de particules. Mais l’erreur humaine reste le maillon faible. Comme le résume un expert, la réalité du terrain est implacable :

80% des non-conformités viennent d’erreurs humaines.

– Dr Bernard, Guide des salles blanches 2026

Cette statistique souligne que la culture de la propreté, la formation rigoureuse et la discipline personnelle sont aussi critiques que les systèmes de filtration d’air. La souveraineté numérique repose donc autant sur la maîtrise des protocoles humains que sur l’investissement dans des infrastructures de pointe.

Problème de coût : comment passer de 50% à 99% de puces fonctionnelles par wafer ?

La question qui hante chaque directeur de fab n’est pas « pouvons-nous le faire ? » mais « pouvons-nous le faire de manière rentable ? ». Le concept clé est le rendement de production (yield). Il s’agit du pourcentage de puces parfaitement fonctionnelles sur une même plaque de silicium (wafer). Dans un secteur où les coûts fixes sont astronomiques, passer d’un rendement de 50% à 95% ne double pas les profits : cela peut faire la différence entre la faillite et la domination du marché.

Fabriquer une seule plaque de silicium de 300 mm, couverte de centaines de puces, implique plus de 1000 étapes de fabrication et coûte plusieurs dizaines de milliers d’euros. Si seulement la moitié des puces fonctionnent, le coût de chaque puce valide double. La « guerre du rendement » est donc au cœur de la compétitivité. C’est une quête obsessionnelle pour éliminer la moindre source de défaut, qu’elle soit liée à une particule (voir section précédente), à une dérive de processus ou à une imperfection du matériau.

Le marché des semi-conducteurs est colossal. Une analyse du Sénat français rappelait déjà il y a quelques années que le secteur des semiconducteurs représente 265 milliards de dollars de chiffre d’affaires mondial, un chiffre en croissance constante. Dans ce contexte, chaque point de rendement gagné se chiffre en millions de dollars. L’amélioration continue du rendement n’est pas une simple optimisation ; c’est une arme stratégique. C’est ce qui permet à des entreprises comme TSMC de produire en masse les puces les plus complexes avec une rentabilité que leurs concurrents peinent à égaler.

La maîtrise du rendement est donc la traduction économique directe de la maîtrise technique. Elle exige une culture de la donnée, où chaque paramètre de chaque machine est monitoré en temps réel pour détecter la moindre déviation. C’est là que l’intelligence artificielle et l’analyse prédictive deviennent des alliés indispensables pour anticiper les pannes et optimiser les réglages en continu.

Plan d’action pour l’amélioration du rendement en production

- Monitoring en temps réel : Implémenter un suivi constant des paramètres critiques de chaque étape du processus pour une détection immédiate des anomalies.

- Analyse prédictive : Utiliser des modèles d’IA pour analyser les données de production et anticiper les dérives avant qu’elles ne provoquent des défauts.

- Métrologie in-situ : Intégrer des outils de mesure directement dans les équipements de production pour corriger les paramètres en cours de fabrication.

- Optimisation du « binning » : Affiner le tri des puces en fin de production pour maximiser la valeur extraite de chaque wafer, même celles qui ne sont pas « parfaites ».

- Protocoles de propreté renforcés : Mener des audits constants des procédures et des formations pour réduire drastiquement la contamination d’origine humaine.

Faisceau d’électrons ou photolithographie : quelle technique pour le prototypage rapide de nanostructures ?

Avant de lancer une production de masse qui coûtera des millions, il est essentiel de pouvoir prototyper et tester de nouvelles architectures de circuits. Pour cette phase critique, deux technologies principales s’affrontent : la photolithographie, reine de la production de masse, et la lithographie par faisceau d’électrons (e-beam), championne de la flexibilité et de la résolution. Le choix dépend d’un arbitrage constant entre vitesse, coût et précision.

La photolithographie utilise la lumière pour transférer un motif depuis un « photomasque » vers une résine photosensible sur le wafer. C’est un processus extrêmement rapide et répétable : une fois le masque fabriqué (ce qui est très coûteux), on peut exposer des milliers de wafers à l’heure. C’est la technique de choix pour la production à grand volume, mais elle manque de flexibilité. Le moindre changement dans le design du circuit exige la fabrication d’un nouveau masque, un processus long et onéreux.

La lithographie par faisceau d’électrons, quant à elle, est une technique « direct write » sans masque. Un faisceau d’électrons très fin, contrôlé par ordinateur, dessine directement le motif dans la résine, pixel par pixel. Sa résolution est bien supérieure à celle de la photolithographie optique, permettant de créer des structures de quelques nanomètres. Surtout, elle offre une flexibilité totale : modifier le dessin du circuit revient simplement à changer un fichier informatique. C’est l’outil idéal pour la recherche et le prototypage rapide.

Étude de cas : Le FIB comme outil de prototypage et d’édition de circuits

Une technologie complémentaire, le Faisceau d’Ions Focalisé (FIB), est également devenue incontournable dans ce domaine. Comme le note un rapport d’Orsay Physics, au cours des 25 dernières années, l’instrumentation FIB est devenue une technologie clé pour de vastes domaines d’applications en science des matériaux, de l’édition de circuits à la préparation d’échantillons TEM, l’analyse microstructurale et le nano-usinage de prototypes. Le FIB permet non seulement de graver des motifs, mais aussi de déposer des conducteurs pour « recâbler » un circuit existant. Un ingénieur peut ainsi tester une modification sur une puce déjà fabriquée sans avoir à relancer tout le processus, accélérant drastiquement les cycles d’innovation.

La souveraineté numérique ne repose pas uniquement sur la capacité à produire en masse, mais aussi sur la capacité à innover rapidement. La maîtrise des techniques de prototypage rapide comme l’e-beam et le FIB est donc un atout stratégique, permettant de réduire les temps de développement et de tester des architectures de rupture avant la concurrence.

Le geste brusque qui coûte 50 000 € de puces électroniques en une seconde

Nous avons parlé des machines, des processus et des particules. Mais au bout de la chaîne, il y a toujours un opérateur humain. En salle blanche, la moindre erreur de manipulation, le moindre geste non maîtrisé, peut avoir des conséquences financières désastreuses. Un wafer de 300 mm en fin de cycle de production peut valoir plusieurs dizaines, voire centaines de milliers d’euros. Le faire tomber ou le rayer, c’est anéantir des semaines de travail et des ressources considérables.

La culture de la salle blanche est une culture de la lenteur et de la précision. Chaque mouvement est délibéré. On ne se déplace pas, on « flotte ». On ne tend pas un objet, on le présente. Cette discipline n’est pas un caprice, c’est une nécessité dictée par deux facteurs : la fragilité extrême du wafer et la nécessité de ne pas générer de particules. Un geste brusque libère des milliers de particules de la combinaison de l’opérateur, contaminant potentiellement toute la zone de travail.

Le témoignage d’un professionnel du secteur pharmaceutique, dont les contraintes sont similaires, est éclairant sur ce point. Il met en lumière la dualité entre la rigueur et l’erreur :

J’ai vu des analyses ruinées par une simple fibre de vêtement ou des audits sauvés par un protocole de nettoyage irréprochable.

– Anonyme, Expérience terrain en salle blanche

Cette réalité est encore plus critique en microélectronique. Alors qu’une salle blanche pour l’industrie pharmaceutique de classe ISO 8 peut tolérer une concentration significative de particules (une norme de propreté ISO 8 autorise jusqu’à 352 000 particules par mètre cube), les fabs de pointe opèrent à des niveaux de propreté des milliers de fois supérieurs. La marge d’erreur humaine est donc quasi nulle. La formation ne se limite pas à l’utilisation des machines ; elle inclut un entraînement quasi chorégraphique aux gestes et postures autorisés. La souveraineté opératoire, c’est aussi cela : la discipline du geste.

À retenir

- La souveraineté numérique est une compétence opérationnelle : elle se mesure au rendement de production, à la maîtrise de la précision et à la discipline humaine en salle blanche.

- L’ennemi principal est invisible et multiple : contamination particulaire, dérives de processus, erreurs de manipulation. Le combattre exige une culture de la rigueur absolue.

- La possession de technologies de pointe comme l’EUV ou le FIB est un prérequis, mais elle est stérile sans le savoir-faire collectif pour les opérer avec une fiabilité proche de 100%.

Comment la lithographie descendante peut-elle encore descendre sous les 5 nanomètres ?

La loi de Moore, qui prédit le doublement du nombre de transistors sur une puce tous les deux ans environ, a été le moteur de l’industrie pendant un demi-siècle. Ce progrès a été rendu possible par une quête incessante de miniaturisation, menée par la photolithographie. Aujourd’hui, nous sommes arrivés à une frontière physique. Graver des motifs de quelques nanomètres avec de la lumière semble défier les lois de l’optique. Pourtant, la course continue, menée par une technologie révolutionnaire : la lithographie par ultraviolets extrêmes (EUV).

La lithographie EUV utilise une « lumière » d’une longueur d’onde extrêmement courte (13,5 nm), bien plus courte que l’ultraviolet profond (DUV) utilisé précédemment. Cette longueur d’onde réduite permet de dessiner des détails beaucoup plus fins. Grâce à elle, la lithographie EUV permet actuellement d’atteindre des nœuds de processus de 5 nm et 3 nm en production. Cependant, la technologie est d’une complexité ahurissante. La lumière EUV est absorbée par presque tout, y compris l’air et les lentilles en verre. Les machines doivent donc opérer sous vide et utiliser une série de miroirs multicouches d’une perfection quasi absolue pour guider et focaliser le faisceau.

La maîtrise de la technologie EUV est aujourd’hui le principal ticket d’entrée dans le club très fermé des fabricants de puces de pointe. Une seule machine EUV, fabriquée quasi-exclusivement par l’entreprise néerlandaise ASML, coûte plus de 150 millions d’euros. En posséder est une chose, savoir l’opérer pour atteindre un rendement élevé en est une autre. C’est un enjeu de souveraineté si critique que la vente de ces machines est soumise à des contrôles géopolitiques stricts.

Étude de cas : La stratégie japonaise avec Rapidus

L’exemple de l’entreprise japonaise Rapidus est emblématique. En s’équipant des dernières machines EUV, le Japon affiche clairement son ambition de revenir au premier plan. Comme l’explique leur direction, Rapidus est devenue la première entreprise au Japon à installer un scanner EUV prêt pour la production. Ce mouvement vers la production de masse de puces logiques 2nm positionne Rapidus comme un acteur critique pour ramener le Japon à l’avant-garde de l’innovation mondiale en semiconducteurs. Cette initiative montre que la souveraineté passe par des investissements technologiques massifs, couplés à une stratégie nationale pour reconstruire un écosystème de compétences.

La prochaine étape est déjà en vue : la lithographie EUV « High-NA » (à haute ouverture numérique), qui promet de graver des structures encore plus fines, sous les 2 nanomètres. La course à la miniaturisation n’est pas terminée, mais chaque nouveau pas coûte exponentiellement plus cher en R&D, en investissement et en complexité opérationnelle.

En définitive, la maîtrise de la chaîne de valeur de la précision est le véritable enjeu. Chaque étape, de la sculpture ionique à la lithographie EUV, est un maillon critique. L’autonomie stratégique ne sera atteinte que par les nations et les entreprises capables de transformer l’excellence scientifique en fiabilité industrielle. L’étape suivante consiste à intégrer ces compétences dans une stratégie de production cohérente et résiliente.