Descendre sous les 5 nm n’est plus une simple question de technologie, mais un arbitrage constant entre la précision physique et la viabilité économique de la production de masse.

- La technologie High-NA EUV offre une résolution théorique inégalée, mais se heurte à un coût par machine et à une complexité opérationnelle (stitching des masques) sans précédent.

- À ces échelles, les défauts stochastiques et les fuites par effet tunnel ne sont plus des exceptions mais des contraintes fondamentales qui dégradent le rendement et forcent des stratégies de contournement (multi-patterning, GAA) qui ont elles-mêmes leurs propres inconvénients.

Recommandation : La clé du succès ne réside pas dans l’adoption d’une solution unique, mais dans l’orchestration de la moins mauvaise combinaison de procédés pour chaque nœud technologique, en évaluant en permanence le compromis entre performance, coût et taux de défauts.

L’obsession de l’industrie des semi-conducteurs pour la loi de Moore, ce métronome qui dicte le doublement de la densité des transistors tous les deux ans, a atteint un point de rupture. Alors que nous nous approchons des limites physiques de la matière, graver des circuits en dessous du seuil symbolique des 5 nanomètres semble relever de la science-fiction. La solution la plus médiatisée, la lithographie par ultraviolets extrêmes (EUV), est souvent présentée comme la réponse définitive. Pourtant, cette vision simplifie à l’extrême une réalité bien plus complexe, faite d’arbitrages techniques et de contraintes économiques vertigineuses.

Et si la question n’était plus de savoir *si* l’on peut graver plus petit, mais à *quel prix* ? Un prix qui ne se mesure pas seulement en millions d’euros par machine, mais en taux de défauts, en complexité des procédés et en rendement de production. Le véritable défi n’est plus une simple course à la miniaturisation, mais une guerre de compromis où chaque nanomètre gagné sur le silicium se paie par une complexité exponentielle dans les salles blanches. Cette bataille se joue sur plusieurs fronts : le choix des matériaux comme les photorésines, la gestion des erreurs stochastiques qui deviennent la norme plutôt que l’exception, et même la remise en question fondamentale de l’approche « descendante » (top-down) qui a prévalu jusqu’ici.

Cet article propose de plonger au cœur de ces arbitrages. Nous analyserons les contraintes physiques et économiques qui définissent aujourd’hui la feuille de route des fondeurs comme Intel, TSMC et Samsung. En déconstruisant les défis un par un, de la physique des machines EUV aux phénomènes quantiques qui se manifestent à l’échelle atomique, nous verrons comment l’industrie orchestre un ensemble de solutions imparfaites pour continuer, malgré tout, à repousser les frontières du possible.

Pour naviguer au cœur de cette complexité technique, cet article décortique les défis et les arbitrages fondamentaux auxquels les ingénieurs sont confrontés. Le sommaire ci-dessous vous guidera à travers les différentes facettes de cette course à la miniaturisation.

Sommaire : Les arbitrages techniques pour graver sous les 5 nanomètres

- Pourquoi la lithographie extrême UV coûte-t-elle 150 millions d’euros par machine ?

- Comment choisir une résine capable de résoudre des motifs de 7nm sans s’effondrer ?

- Faisceau d’électrons ou photolithographie : quelle technique pour le prototypage rapide de nanostructures ?

- L’erreur de gravure qui provoque des courts-circuits aléatoires sur les puces avancées

- Dans quel ordre empiler les masques pour éviter les erreurs d’alignement critiques ?

- Pourquoi les électrons traversent-ils les murs isolants quand les transistors deviennent trop petits ?

- Attaque chimique liquide ou bombardement ionique : quel choix pour des murs verticaux parfaits ?

- Pourquoi l’assemblage ascendant est-il le futur incontournable de la fabrication de composants moléculaires ?

Pourquoi la lithographie extrême UV coûte-t-elle 150 millions d’euros par machine ?

Le coût exorbitant d’une machine de lithographie EUV, qui atteint désormais près de 350 millions d’euros pour les derniers modèles High-NA, n’est pas le fruit du hasard mais la conséquence directe de défis physiques extrêmes. Contrairement à la lumière visible, les rayons EUV (d’une longueur d’onde de 13,5 nm) sont absorbés par presque tous les matériaux, y compris l’air et le verre des lentilles traditionnelles. La fabrication d’une machine EUV requiert donc un environnement de vide quasi parfait et un système optique entièrement basé sur des miroirs. Et pas n’importe quels miroirs.

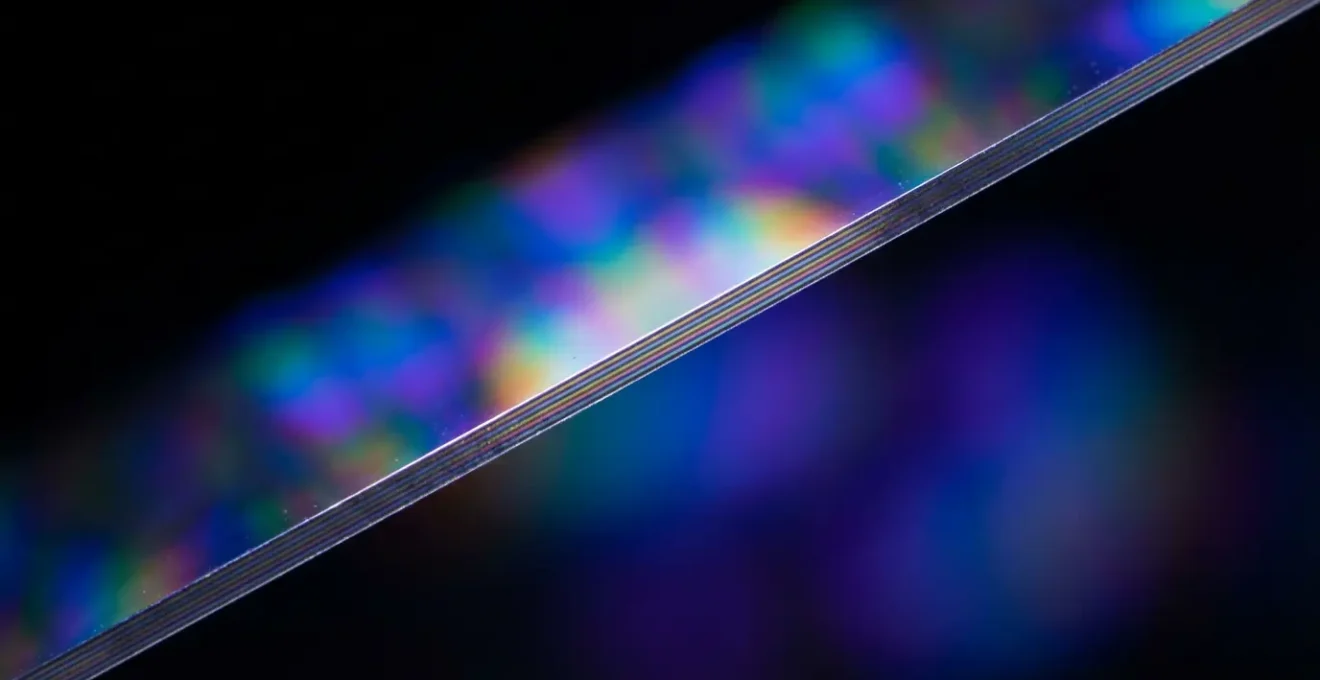

Le cœur technologique de ces machines réside dans leurs miroirs de Bragg multicouches. Chaque miroir est constitué d’une alternance de plusieurs dizaines de couches de silicium et de molybdène, dont l’épaisseur est contrôlée avec une précision picométrique (soit un millième de nanomètre). Ces surfaces sont considérées comme les objets les plus lisses et les plus précis jamais fabriqués par l’homme. La moindre imperfection dévierait le faisceau lumineux et rendrait toute gravure impossible. Cette prouesse technique explique la position de quasi-monopole d’ASML, qui pèse environ 80 % du marché et dont la technologie est indispensable pour toutes les puces de 5 nm et moins.

Comme le montre ce système optique complexe, le prix d’une machine EUV reflète non seulement les coûts de R&D colossaux, mais aussi les 18 mois nécessaires à l’assemblage de ses centaines de milliers de composants. Il s’agit moins d’un produit que d’un projet d’ingénierie fondamentale, où chaque machine est une infrastructure stratégique. Ce coût initial massif constitue le premier arbitrage pour les fondeurs : investir des milliards pour rester dans la course technologique ou se concentrer sur des nœuds de gravure plus matures et rentables.

Comment choisir une résine capable de résoudre des motifs de 7nm sans s’effondrer ?

Avoir une source lumineuse d’une extrême finesse ne sert à rien si le « papier » sur lequel on imprime n’est pas capable d’enregistrer le motif avec la même précision. Ce « papier », c’est la photorésine (ou « photoresist »), une fine couche de polymère sensible à la lumière déposée sur le wafer de silicium. Pour les nœuds inférieurs à 10 nm, le choix de la résine devient un arbitrage critique, résumé par le triptyque RLS : Résolution, Linéarité (Line Edge Roughness), et Sensibilité. Une résine très sensible réagit vite à la lumière (bon pour le débit), mais a souvent une résolution plus faible et des bords de motifs plus « rugueux ».

Le défi majeur à ces échelles est d’ordre mécanique : l’effondrement des motifs. Lorsque l’on grave des lignes de quelques nanomètres de large, le ratio entre leur hauteur et leur largeur (l’aspect ratio) devient très élevé. Ces murs extrêmement fins et hauts, une fois la résine développée, peuvent s’effondrer ou se coller les uns aux autres sous l’effet des forces de tension de surface lors du séchage. Pour contrer ce phénomène, les chimistes développent des résines à base de métal (Metal-Oxide Resists – MOR) qui offrent une meilleure rigidité structurelle que les résines organiques traditionnelles (Chemically Amplified Resists – CAR).

L’arrivée des systèmes High-NA, capables d’atteindre une dimension critique (CD) de 8 nm contre 13 nm pour les systèmes EUV standards, met encore plus de pression sur les fournisseurs de résines. La performance n’est plus seulement une question d’optique, mais une synergie entre la machine et le matériau. Comme le soulignait un communiqué d’ASML, même si des finesses extrêmes sont possibles avec les machines actuelles, c’est souvent au prix d’un « processus de production complexe qui augmente les coûts et les risques de défaut ».

Certes, ces finesses de gravure sont possibles avec les machines actuelles, mais seulement par l’intermédiaire d’un processus de production complexe qui augmente les coûts et les risques de défaut.

– ASML, Communiqué de presse ASML

Le choix de la résine est donc un compromis permanent entre la performance physique (résolution, rigidité) et la réalité industrielle (vitesse, coût, rendement). Une résine miracle n’existe pas ; il n’existe que la meilleure résine pour un procédé et un motif donnés.

Faisceau d’électrons ou photolithographie : quelle technique pour le prototypage rapide de nanostructures ?

Si la photolithographie EUV est la reine de la production de masse, elle est extrêmement rigide pour la recherche et le prototypage. La fabrication d’un jeu de masques pour un seul design de puce peut coûter plus de 100 millions d’euros et prendre des semaines. Pour le développement de nouvelles architectures ou la production en très petits volumes, d’autres techniques offrent un arbitrage différent entre vitesse, coût et résolution. La lithographie par faisceau d’électrons (e-beam) et la lithographie par nanoimpression (NIL) sont les deux principales alternatives.

La lithographie e-beam fonctionne comme un stylo : un faisceau d’électrons très fin « dessine » directement le motif sur la résine, sans aucun masque. Cette approche « direct-write » offre une flexibilité maximale et une résolution qui peut descendre sous les 10 nm. Cependant, son débit est extrêmement faible, car elle dessine le motif pixel par pixel. Elle est donc inutilisable pour la production de masse mais reste l’outil de choix pour la R&D et la fabrication de masques.

Une autre alternative, sur laquelle mise notamment Canon, est la nanoimpression (NIL). Le principe est plus proche du gaufrage : un moule (ou « template ») portant le motif en relief est pressé dans une résine, qui durcit ensuite. Cette technique promet des coûts bien plus bas que l’EUV, car les machines sont plus simples. Elle reste cependant dépendante d’un moule physique et pose des défis en termes de défauts et d’alignement des couches successives. Récemment, Canon a lancé ses premières machines NIL capables de graver en 5 nm, se positionnant comme un concurrent direct d’ASML sur certains segments de marché.

Le tableau suivant résume les arbitrages clés entre ces différentes techniques de lithographie pour le prototypage et la production. Ces données sont basées sur une synthèse d’informations publiques, notamment des analyses disponibles sur des plateformes comme Wikipedia pour la lithographie e-beam.

| Critère | Lithographie e-beam | Photolithographie EUV | Nanoimpression (NIL) |

|---|---|---|---|

| Résolution minimale | < 10 nm | 7-13 nm | 10-20 nm |

| Débit (wafers/h) | < 10 | 100-185 | 20-40 |

| Coût par wafer | Très élevé | Élevé | Modéré |

| Besoin de masque | Non (direct-write) | Oui (150 M€/set) | Oui (moule) |

| Flexibilité design | Maximale | Limitée | Moyenne |

L’erreur de gravure qui provoque des courts-circuits aléatoires sur les puces avancées

À l’échelle nanométrique, la prévisibilité s’effondre. Le défi le plus insidieux pour les ingénieurs n’est plus l’erreur systématique, que l’on peut corriger, mais le défaut stochastique : une erreur aléatoire et imprévisible qui apparaît sur une puce mais pas sur sa voisine, alors qu’elles ont été fabriquées dans des conditions identiques. Ces défauts peuvent prendre la forme d’un pont de résine non désiré créant un court-circuit, ou d’une ligne brisée coupant une connexion. Leur nature aléatoire les rend cauchemardesques à détecter et à corriger, et ils sont la principale cause de la baisse du rendement (yield) sur les nœuds avancés.

Ces défauts sont exacerbés par les techniques de contournement comme le multi-patterning. Lorsque la résolution d’une machine ne suffit pas pour graver un motif dense, on le décompose en plusieurs motifs plus simples, gravés en plusieurs étapes successives. Cette technique permet d’utiliser des machines plus anciennes pour des nœuds plus fins, mais chaque étape ajoute des risques d’erreurs d’alignement et de variations de procédé. Selon certaines analyses, le multi-patterning augmente les taux de défauts et rallonge les cycles de production de 30 à 40%.

Face à ce mur stochastique, les stratégies divergent. Intel, par exemple, a fait le pari d’être le premier client des machines High-NA EUV d’ASML. En investissant massivement dans cette nouvelle génération de machines, Intel vise à réduire sa dépendance au multi-patterning pour ses futurs nœuds (comme l’Intel 14A, soit 1,4 nm), espérant ainsi obtenir un meilleur rendement et reprendre son leadership technologique. C’est une stratégie de « first-mover » à haut risque et à haut potentiel de récompense, où la maîtrise de la nouvelle technologie est vue comme la solution pour maîtriser le chaos stochastique.

Plan d’action : Audit des sources de défauts stochastiques

- Points de contact : Lister tous les points du procédé où la résine interagit avec d’autres matériaux (adhésion au substrat, interaction avec les gaz de gravure).

- Collecte : Inventorier les types de défauts observés (ponts, lignes brisées, trous) via imagerie MEB (Microscope Électronique à Balayage) sur des wafers de test.

- Cohérence : Confronter la fréquence des défauts aux variations de paramètres du procédé (dose d’exposition, temps de développement, température).

- Mémorabilité/émotion : Identifier les « signatures » de défauts : certains sont-ils systématiquement liés à une zone du wafer ou à une configuration de motifs spécifique ?

- Plan d’intégration : Établir des règles de conception (Design for Manufacturing) pour éviter les motifs les plus à risque et ajuster les paramètres du procédé pour les zones critiques.

Dans quel ordre empiler les masques pour éviter les erreurs d’alignement critiques ?

Une puce moderne est une structure tridimensionnelle complexe, un gratte-ciel de plusieurs dizaines de couches de circuits interconnectées. Chaque couche est gravée à l’aide d’un masque différent, et l’alignement de ces masques les uns sur les autres doit être parfait, avec une tolérance de l’ordre du nanomètre. Une erreur d’alignement (overlay error) même minime peut provoquer des courts-circuits ou des circuits ouverts, rendant la puce inutilisable. Ce défi est amplifié par les nouvelles contraintes des machines High-NA EUV.

Paradoxalement, pour obtenir une meilleure résolution, les systèmes High-NA EUV utilisent une optique qui réduit de moitié le champ d’exposition sur le wafer. Conséquence : il faut deux expositions, côte à côte, pour couvrir la même surface qu’une seule exposition avec une machine EUV standard. Cette technique, appelée « stitching » (couture), introduit une nouvelle source d’erreur critique à l’interface entre les deux champs exposés. Assurer une continuité parfaite des motifs à travers cette « couture » est un casse-tête d’ingénierie qui s’ajoute aux défis d’alignement entre les couches. Bien que la densité soit 2,9 fois supérieure avec le High-NA, cette complexité est le prix à payer.

Face à cet enjeu, les stratégies des fondeurs divergent, illustrant à nouveau la guerre des compromis. Alors qu’Intel mise sur le High-NA, son concurrent direct TSMC a adopté une stratégie plus conservatrice pour son nœud A16 (1,6 nm). TSMC a choisi de maximiser l’utilisation de sa flotte de machines EUV Low-NA existantes, en repoussant les limites du multi-patterning et des techniques avancées de « pattern shaping ». Cette approche de « délai calculé » permet à TSMC de capitaliser sur une technologie qu’il maîtrise parfaitement, évitant les risques et la courbe d’apprentissage abrupte du High-NA et du stitching, tout en continuant à faire progresser la densité. C’est un pari sur la maîtrise des procédés complexes plutôt que sur l’adoption de la dernière rupture matérielle.

La question de l’ordre d’empilement des masques devient alors une décision stratégique. Faut-il graver les couches les plus critiques en premier ? Comment décomposer les motifs pour minimiser les risques d’erreurs d’alignement et de stitching ? Il n’y a pas de réponse unique, seulement une optimisation spécifique à chaque design de puce et à chaque stratégie de production.

Pourquoi les électrons traversent-ils les murs isolants quand les transistors deviennent trop petits ?

En descendant sous la barre des 5 nm, les ingénieurs ne se heurtent plus seulement à des défis de fabrication, mais aux lois étranges de la physique quantique. Le phénomène le plus problématique est l’effet tunnel quantique. En physique classique, un électron est comme une bille : s’il n’a pas assez d’énergie pour franchir un mur (une barrière isolante), il rebondit. En physique quantique, l’électron se comporte aussi comme une onde. Il a une probabilité non nulle de « traverser » le mur, même sans avoir l’énergie nécessaire. Plus le mur est fin, plus cette probabilité augmente.

Dans un transistor, les murs isolants (la grille d’oxyde) sont devenus si fins – quelques atomes d’épaisseur – que les électrons s’en « échappent ». Cette fuite de courant, même lorsque le transistor est censé être éteint, entraîne une surconsommation d’énergie et une surchauffe de la puce. C’est une des raisons fondamentales pour lesquelles la simple miniaturisation de l’architecture traditionnelle (FinFET) atteint ses limites. Alors que nous approchons du ‘mur des 2 atomes’, ce phénomène n’est plus marginal mais dominant.

La parade à ce fléau quantique n’est pas une solution unique, mais une orchestration de plusieurs innovations. Comme le souligne une analyse de l’industrie, la lithographie High-NA n’est qu’une partie de la réponse.

Le High-NA, combiné avec l’architecture de transistor Gate-All-Around (GAA) et la distribution d’énergie par l’arrière, fournit la précision nécessaire pour naviguer dans ces défis au niveau quantique. Cela garantit que l’industrie peut continuer à entasser plus de transistors sur une seule puce.

– Analyse TokenRing, The $350 Million Heartbeat of the AI Revolution

L’architecture Gate-All-Around (GAA), qui remplace le FinFET, est une réponse directe à l’effet tunnel. Au lieu d’une grille contrôlant le canal sur trois côtés, la grille entoure complètement le canal de silicium. Ce contrôle renforcé « pince » plus efficacement le flux d’électrons, réduisant drastiquement les fuites. La lithographie de précision est donc nécessaire non pas pour violer les lois de la physique, mais pour construire les structures (comme les GAA) qui permettent de les contourner intelligemment.

Attaque chimique liquide ou bombardement ionique : quel choix pour des murs verticaux parfaits ?

Une fois le motif imprimé dans la résine par la lithographie, il faut « sculpter » le silicium en dessous. Cette étape, appelée gravure (etching), est aussi critique que la lithographie elle-même. L’objectif est de creuser des tranchées avec des parois parfaitement verticales. Le moindre angle ou la moindre rugosité sur ces parois peut dégrader les performances électriques du transistor. Pour ce faire, deux grandes méthodes s’opposent : la gravure humide (wet etching) et la gravure sèche (dry etching).

La gravure humide utilise des bains chimiques (comme l’acide fluorhydrique) pour dissoudre la matière. C’est un procédé isotrope, c’est-à-dire qu’il grave dans toutes les directions à la même vitesse. Il a donc tendance à creuser sous la résine, créant des profils arrondis et des parois en pente, ce qui est inacceptable pour les motifs sub-10 nm. Son usage est aujourd’hui limité à des nettoyages ou à la gravure de motifs larges et peu critiques.

La gravure sèche, et plus spécifiquement la gravure par ions réactifs (Reactive Ion Etching – RIE), est la méthode de choix pour la haute précision. Dans une chambre à vide, un plasma est créé. Des ions énergétiques sont alors accélérés et bombardent la surface du wafer dans une direction purement verticale. Ce bombardement physique casse les liaisons du silicium, tandis que les radicaux chimiques du plasma réagissent avec la matière pour l’évacuer sous forme de gaz. Ce procédé est hautement anisotrope et permet d’obtenir des parois quasi-parfaites. L’arbitrage se fait sur le choix des gaz, la puissance du plasma et la température, qui doivent être ajustés pour maximiser la verticalité tout en minimisant les dommages au substrat.

L’évolution de la lithographie a un impact direct sur la gravure. La feuille de route d’ASML, qui prévoit une ouverture numérique passant de 0,33 (EUV standard) à 0,55 (High-NA) puis 0,75+ (Hyper-NA), signifie que les motifs à graver seront de plus en plus fins et denses. La précision du « pinceau » lumineux exige un « ciseau » de gravure d’une finesse équivalente, rendant la maîtrise des procédés de gravure sèche encore plus stratégique.

À retenir

- La viabilité économique de la production de masse est devenue un facteur aussi limitant que les contraintes physiques, avec des machines coûtant plus de 350 millions d’euros.

- La performance ne dépend plus d’une seule technologie, mais d’une orchestration complexe de solutions (High-NA, résines, GAA, gravure) pour contourner les obstacles physiques comme les défauts stochastiques et l’effet tunnel.

- Les stratégies des leaders industriels (Intel vs TSMC) divergent, illustrant qu’il n’y a pas de solution unique mais des arbitrages différents entre risque technologique, maîtrise des procédés existants et coût.

Pourquoi l’assemblage ascendant est-il le futur incontournable de la fabrication de composants moléculaires ?

La lithographie, par nature, est une approche « descendante » (top-down) : on part d’un bloc de matière (le wafer de silicium) et on y sculpte des motifs en enlevant de la matière. Cette méthode, bien que perfectionnée à l’extrême, se heurte inévitablement à des limites fondamentales, qu’elles soient physiques (taille des atomes, effets quantiques) ou économiques (coût exponentiel des usines et des machines). Face à ce mur, une autre philosophie gagne du terrain dans les laboratoires : l’approche « ascendante » (bottom-up).

L’idée de l’assemblage ascendant est de construire les structures non pas en gravant, mais en assemblant les composants atome par atome ou molécule par molécule, à la manière dont la nature construit le vivant. Des techniques comme le dépôt de couches atomiques (Atomic Layer Deposition – ALD) ou la manipulation d’atomes individuels avec des microscopes à effet tunnel (STM) sont des exemples de cette approche. Le potentiel est immense : créer des matériaux et des dispositifs avec une perfection atomique, sans les défauts inhérents aux procédés de gravure.

Cependant, si cette approche est prometteuse pour fabriquer des composants moléculaires uniques ou des surfaces parfaites, son passage à une production de masse est un défi colossal. Les procédés sont aujourd’hui extrêmement lents et coûteux. L’assemblage ascendant n’est donc pas un remplaçant à court ou moyen terme pour la lithographie, mais plutôt une voie complémentaire et un objectif à long terme pour l’ère « post-Moore ». La pression économique pour trouver des alternatives est immense. La demande en puissance de calcul, tirée par l’intelligence artificielle, pousse les revenus de l’industrie à des sommets, comme en témoigne le CEO d’ASML, Christophe Fouquet, qui déclarait que « la croissance de l’intelligence artificielle est le moteur clé de la croissance dans notre industrie ».

Cette manne financière justifie les investissements massifs, non seulement dans l’amélioration de la lithographie descendante, mais aussi dans l’exploration de ces voies de rupture. Le futur de la fabrication de composants ne résidera probablement pas dans le triomphe d’une approche sur l’autre, mais dans une hybridation intelligente, où la lithographie créera l’échafaudage global et l’assemblage ascendant viendra y placer, avec une précision atomique, les composants les plus critiques.

Pour les fabricants et les ingénieurs, l’enjeu est donc d’évaluer en continu cette myriade de compromis technologiques. Définir une feuille de route de production qui soit à la fois ambitieuse sur le plan de la performance et réaliste sur le plan du rendement et des coûts est le véritable défi pour continuer à faire vivre la loi de Moore.